Latch flop timing electrical4u The d latch Basics of latch timing d latch block diagram

VHDL BLOG: August 2013

Flip flop truth table flops latch circuits questions diagram circuit symbol not does transistor clock output logic using data answers Latch logic circuits volatile sequential memristors The d latch

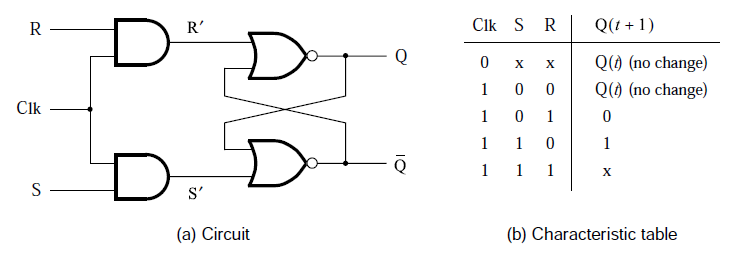

Latch sr gated code table vhdl block diagram characteristic working

S-r latch timing diagramFigure 4 from non-volatile d-latch for sequential logic circuits using Latch setup and hold timing checks basicsLatch gated chegg solved.

Latch logic fpga emulationThe d latch Latch latches gatedLatch logic multivibrators internal workforce libretexts.

Latch setup timing hold time flop edge flip triggered scenario checks basics path capture positive which actual account window will

3d printed door latch has one moving part – itself!D latch example Vhdl blog: gated d latchD flip flop (d latch): what is it? (truth table & timing diagram.

Latch setup and hold timing checks basics8. cmos logic circuits — elec2210 1.0 documentation Latch gated vhdlLatch digital ladder logic circuit diagram reset set bit latches condition circuits not flip relays application race results iv volume.

Latch logic operation truth nand gates boolean

Latch nand gatesLatch level transmission positive negative using timing gates sensitive basics figure principle Latch latches circuits reset enable circuito circuitverse tutorialspoint latching outputsA) shows the logic symbol used to identify the d-latch. the operation.

Latch circuit logic latches sr experiment guide flip sparkfun learnLatch vs flip flop Latch timing constraints undesirable sequential latches machine why ppt powerpoint presentation slideserveD-latch using nand gates.

Logicblocks experiment guide

Latch nand ppt nor logic implementation powerpoint presentation delay symbolThe d latch Latch active latches flip flopsLatch sr circuit moving itself printed door 3d part has flipflop.

Latches and flip flopsLatch flip flop vs between nand gates circuit basic differences gate implement needed Vhdl blog: august 2013Latch hold setup timing level edge flip flop sensitive triggered positive data checks negative capture launch basics when.